## **METHODOLOGY AND ECOSYSTEM**

## FOR THE DESIGN OF A

## **COMPLEX NETWORK ASIC**

vorgelegt von

Sven Uwe Kapferer (Diplom-Informatiker der Technischen Informatik)

aus Mannheim

Mannheim, 2012

Dekan:Prof. Dr. Heinz Jürgen Müller, Universität MannheimReferent:Prof. Dr. Ulrich Brüning, Universität HeidelbergKorreferent:Prof. Dr. Holger Fröning, Universität Heidelberg

Tag der mündlichen Prüfung: 14.02.2013

## Abstract

Performance of HPC systems has risen steadily. While the 10 Petaflop/s barrier has been breached in the year 2011 the next large step into the exascale era is expected sometime between the years 2018 and 2020. The EXTOLL project will be an integral part in this venture. Originally designed as a research project on FPGA basis it will make the transition to an ASIC to improve its already excelling performance even further. This transition poses many challenges that will be presented in this thesis. Nowadays, it is not enough to look only at single components in a system. EXTOLL is part of complex ecosystem which must be optimized overall since everything is tightly interwoven and disregarding some aspects can cause the whole system either to work with limited performance or even to fail.

This thesis examines four different aspects in the design hierarchy and proposes efficient solutions or improvements for each of them. At first it takes a look at the design implementation and the differences between FPGA and ASIC design. It introduces a methodology to equip all on-chip memory with ECC logic automatically without the user's input and in a transparent way so that the underlying code that uses the memory does not have to be changed. In the next step the floorplanning process is analyzed and an iterative solution is worked out based on physical and logical constraints of the EXTOLL design. Besides, a work flow for collaborative design is presented that allows multiple users to work on the design concurrently. The third part concentrates on the high-speed signal path from the chip to the connector and how it is affected by technological limitations. All constraints are analyzed and a package layout for the EXTOLL chip is proposed that is seen as the optimal solution. The last part develops a cost model for wafer and package level test and raises technological concerns that will affect the testing methodology. In order to run testing internally it proposes the development of a stand-alone test platform that is able to test packaged EXTOLL chips in every aspect.

## Zusammenfassung

Die Leistung von HPC Systemen hat sich kontinuierlich gesteigert. Im Jahr 2011 wurde die 10 Petaflop/s Grenze durchbrochen. Der nächste große Schritt in das Exascale Zeitalter wird nun für irgendwann zwischen den Jahren 2018 und 2020 erwartet. Das EXTOLL Projekt wird ein wesentlicher Bestandteil auf dem Weg dorthin sein. Ursprünglich für FPGA Technologie entwickelt wird im nächsten Schritt die Umsetzung als ASIC verwirklicht, um die schon jetzt ausgezeichnete Leistung noch weiter zu steigern. Dieser Wechsel birgt viele Herausforderungen, die in dieser Arbeit vorgestellt werden. Heutzutage genügt es nicht, nur die Einzelkomponenten eines Systems zu betrachten. EXTOLL ist ein Teil eines komplexen Ganzen und muss an allen Stellen optimiert werden, da alle Einzelteile eng miteinander verbunden sind. Die Vernachlässigung einzelner Aspekte kann dazu führen, dass das Gesamtsystem entweder nur mit begrenzter Leistung oder vielleicht sogar gar nicht funktioniert.

Diese Arbeit untersucht vier unterschiedliche Aspekte im Designablauf und stellt für jeden dieser Aspekte eine effiziente Lösung oder Verbesserung vor. Zuerst wird die Umsetzung des Designs betrachtet und die Unterschiede zwischen einem FPGA und einem ASIC Design. Es wird eine Methodik vorgestellt, um den Speicher auf dem Chip automatisch und ohne Zutun des Benutzers mit ECC Logik auszustatten und zwar so, dass der Code, der den Speicher nicht geändert werden muss. Im nächsten Schritt wird der Ablauf des benutzt, Floorplanning analysiert und eine iterative Lösung des Problems basierend auf den technischen und internen Randbedingungen herausgearbeitet. Außerdem wird ein Arbeitsablauf für gemeinschaftliches Arbeiten vorgestellt, der es mehreren Benutzern erlaubt, gleichzeitig am Design zu arbeiten. Der dritte Teil konzentriert sich auf den Hochgeschwindigkeitspfad vom Chip bis zum Stecker und welchen Einfluss die technologischen Einschränkungen auf ihn haben. Alle Bedingungen werden analysiert und ein Entwurf eines Package für den EXTOLL Chip wird aufgezeigt, der als bestmögliche Lösung angesehen wird. Im letzten Teil wird ein Kostenmodell für Tests auf dem Wafer und im Package entwickelt. Es werden technologische Bedenken geäußert, die Einfluss auf den Testablauf haben. Um Tests im Labor selbst durchführen zu können, wird die Entwicklung einer selbständigen Testplattform vorgeschlagen, die es erlaubt fertige EXTOLL Chips nach allen Gesichtspunkten zu testen.

# **Table of Contents**

| 1 | Intr  | oduction                     | . 1 |

|---|-------|------------------------------|-----|

|   | 1.1   | Motivation                   | 1   |

|   | 1.2   | Scope of Work                | 3   |

|   | 1.3   | EXTOLL Design                | 4   |

|   | 1.3.1 | Host Interface               | 5   |

|   | 1.3.2 | EXTOLL Core Logic            | 6   |

|   | 1.3.3 | EXTOLL NIC                   | 8   |

|   | 1.4   | Outline                      | 8   |

|   |       |                              |     |

| 2 | EXT   | OLL ASIC                     | 11  |

|   | 2.1   | Design Decisions             | 11  |

|   | 2.1.1 | Performance Comparison       | 11  |

|   | 2.1.2 | 2 Technology Analysis        | 12  |

|   | 2.2   | Transition from FPGA to ASIC | 17  |

|   | 2.3   | Design Guidelines            | 17  |

|   | 2.3.1 | Timing Basics                | 18  |

|   | 2.3.2 | Reset                        | 19  |

|   | 2.4   | Embedded Memory              | 21  |

|   | 2.4.1 | Memory Faults                | 23  |

|   | 2.4.2 | 2 Automatic Memory Generator | 26  |

|   | 2.5   | Design for Test              | 31  |

|   | 2.6   | Clocking                     | 32  |

|   | 2.6.1 | Supporting Circuits          | 33  |

|   | 2.6.2 | 2 Clocking Structure         | 35  |

|   | 2.6.3 | 9 PLL                        | 37  |

|   | 2.7   | Prototyping                                      | 38         |

|---|-------|--------------------------------------------------|------------|

|   | 2.8   | Toplevel Organization                            | 41         |

| 3 | ASI   | C Design Considerations4                         | <b>1</b> 7 |

|   | 3.1   | Design Preparation                               | 47         |

|   | 3.1.1 | LIB                                              | 47         |

|   | 3.1.2 | LEF                                              | 48         |

|   | 3.1.3 | Capacitance Tables                               | 49         |

|   | 3.1.4 | SDC / Timing Constraints                         | 50         |

|   | 3.1.5 | 5 DEF                                            | 51         |

|   | 3.1.6 | Flow Script                                      | 51         |

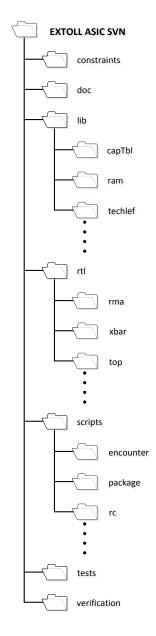

|   | 3.2   | Data Hierarchy                                   | 52         |

|   | 3.3   | Frontend Flow                                    | 54         |

|   | 3.4   | Backend Flow                                     | 50         |

|   | 3.5   | Floorplanning and Datapath Analysis              | 53         |

|   | 3.5.1 | Datapath Analysis - Global View                  | 56         |

|   | 3.5.2 | Pre-placement                                    | 57         |

|   | 3.5.3 | Datapath Analysis - Detailed View                | 59         |

|   | 3.5.4 | Miniature Optimizations                          | 74         |

|   |       |                                                  |            |

| 4 | Opti  | imization of Complex Interconnection Structures7 | 79         |

|   | 4.1   | Design constraints                               | 79         |

|   | 4.1.1 | Technological Limitations                        | 30         |

|   | 4.1.2 | 2 Signal Integrity                               | 30         |

|   | 4.1.3 | Viability                                        | 30         |

|   | 4.1.4 | Economic Feasibility                             | 30         |

|   | 4.2   | Design Components                                | 31         |

|   | 4.2.1 | Connector                                        | 81         |

|   | 4.2.2 | 2 PCB                        | 83   |

|---|-------|------------------------------|------|

|   | 4.2.3 | 3 Package                    | 86   |

|   | 4.2.4 | 4 Die                        | 90   |

|   | 4.3   | Automatic Generation         | 91   |

|   | 4.4   | SI Analysis                  | 92   |

|   | 4.5   | PDN Design                   | 93   |

|   | 4.6   | Results                      | 95   |

|   | 4.6.1 | 1 EXTOLL I/O                 | 95   |

|   | 4.6.2 | 2 EXTOLL Supply              | .101 |

|   | 4.6.3 | 3 Constraints and Efficiency | .103 |

|   |       |                              |      |

| 5 | EXT   | ГОLL Test                    | 105  |

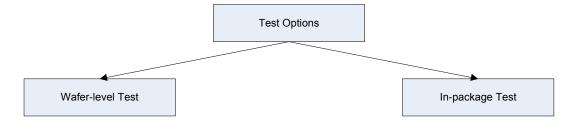

|   | 5.1   | Test Analysis                | 105  |

|   | 5.2   | Wafer Test                   | 107  |

|   | 5.3   | Package Test                 | 108  |

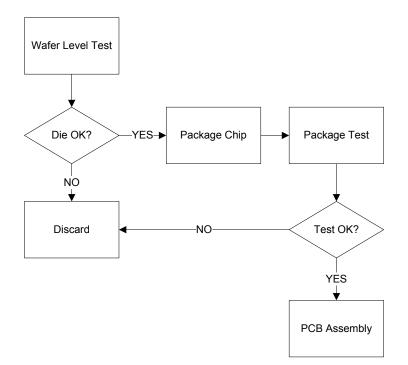

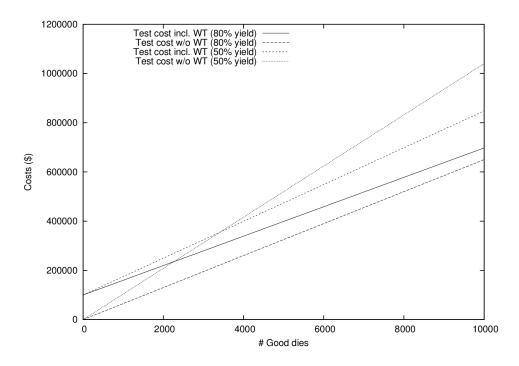

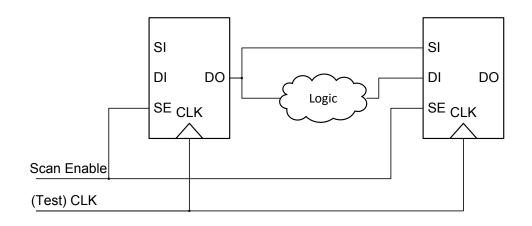

|   | 5.4   | Process Analysis             | 109  |

|   | 5.5   | Test Setup                   | 113  |

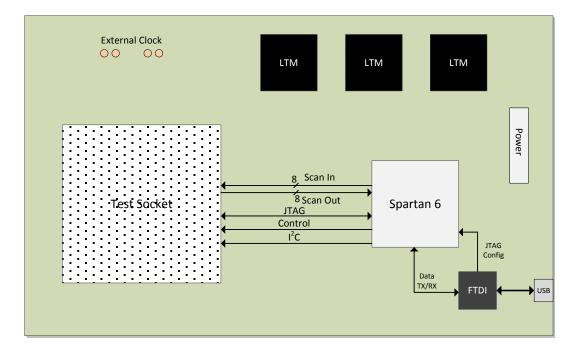

|   | 5.6   | Test Hardware                | 116  |

|   | 5.6.1 | 1 Analysis                   | 116  |

|   | 5.6.2 | 2 Proposal                   | 120  |

|   |       |                              |      |

| 6 | Con   | nclusion                     | 125  |

|   | 6.1   | Results                      | 125  |

|   | 6.2   | Project Review               | 127  |

|   | 6.3   | Outlook                      | 128  |

|   |       |                              |      |

| A | Acre  | onyms                        | 131  |

| В | Bibliography137   |

|---|-------------------|

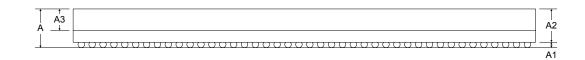

| С | EXTOLL Package147 |

| D | STIL Example      |

# **List of Figures**

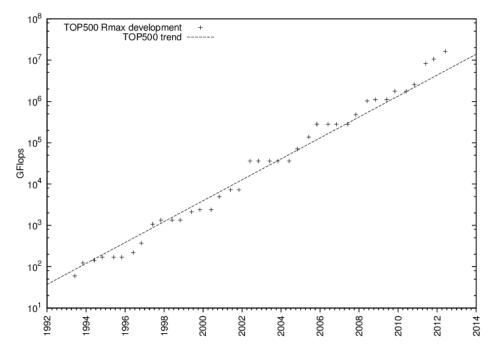

| Figure 1.1 TOP500 Development                                   | 1  |

|-----------------------------------------------------------------|----|

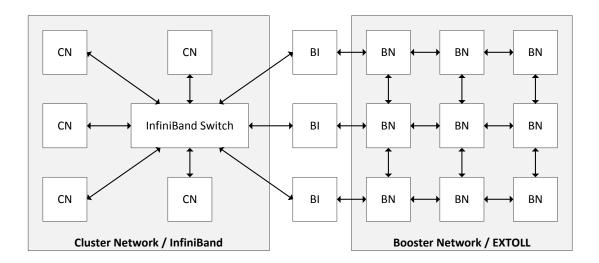

| Figure 1.2 DEEP Architecture                                    | 2  |

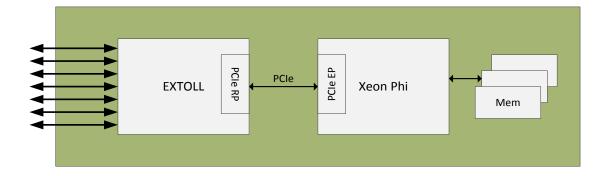

| Figure 1.3 Booster Node Architecture                            | 3  |

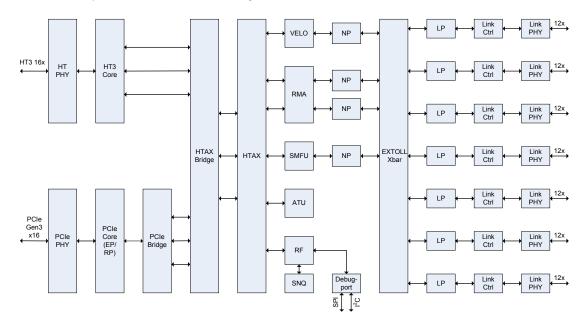

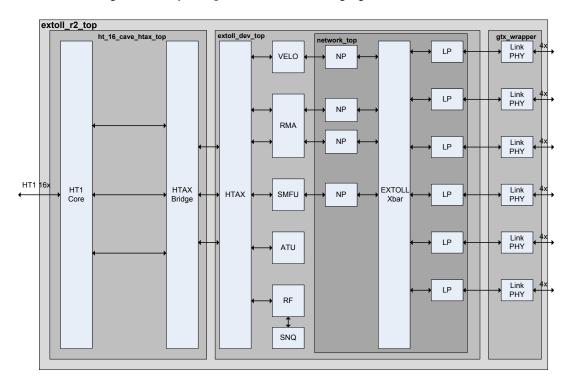

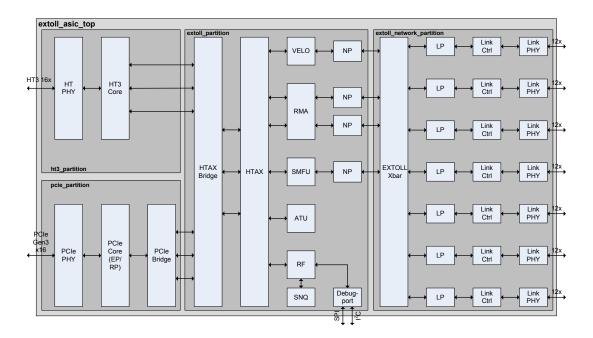

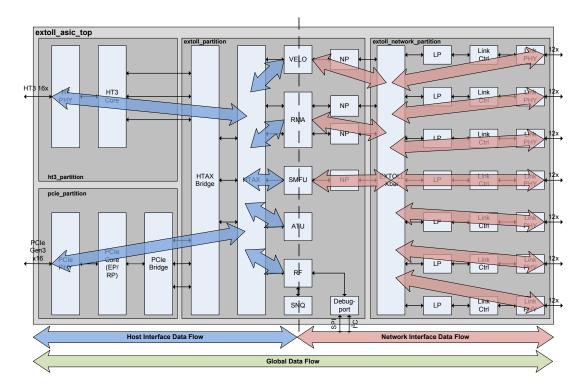

| Figure 1.4 EXTOLL Block Diagram                                 | 5  |

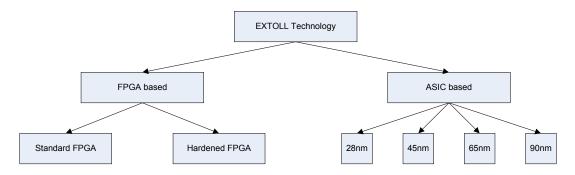

| Figure 2.1 Design Space Diagram for EXTOLL Technology Selection | 13 |

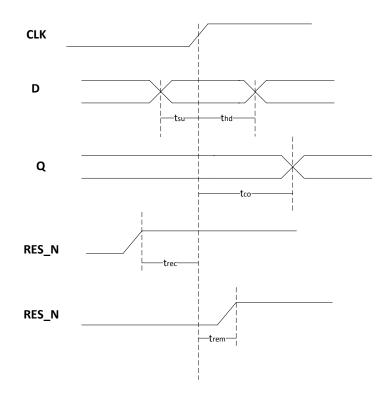

| Figure 2.2 Flip-Flop Timing Parameters                          | 18 |

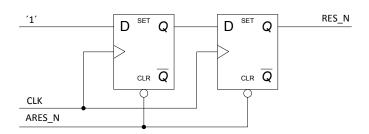

| Figure 2.3 Reset Synchronizer Circuit                           | 20 |

| Figure 2.4 FPGA Memory Flow                                     | 21 |

| Figure 2.5 Memory Size Distribution                             | 22 |

| Figure 2.6 Memory Speed Analysis                                | 23 |

| Figure 2.7 Occupied Chip Area                                   | 24 |

| Figure 2.8 ECC Complexity Analysis                              | 26 |

| Figure 2.9 256x128 RAM Instance                                 | 27 |

| Figure 2.10 RAM Timing with Handshaking                         | 29 |

| Figure 2.11 Levels of Indirection                               | 29 |

| Figure 2.12 Debug Port Overview                                 | 32 |

| Figure 2.13 Divide-by-3 Clock Divider                           |    |

| Figure 2.14 Divide-by-3 Clock Divider Waveform                  | 33 |

| Figure 2.15 Divide-by-5 Clock Divider                           | 34 |

| Figure 2.16 Divide-by-5 Clock Divider Waveform                  | 34 |

| Figure 2.17 Glitchless Clock Multiplexer Waveform               | 34 |

| Figure 2.18 Glitchless Clock Multiplexer                        | 35 |

| Figure 2.19 EXTOLL Clocking Scheme                              | 36 |

| Figure 2.20 EXTOLL PLL                                          |    |

| Figure 2.21 Ventoux Prototyping Platform                    |    |

|-------------------------------------------------------------|----|

| Figure 2.22 Galibier Prototyping Platform                   |    |

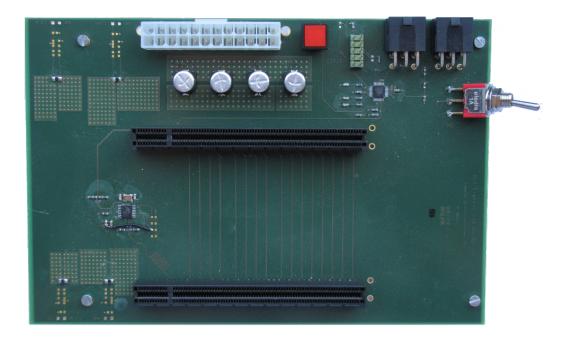

| Figure 2.23 PCIe Backplane                                  |    |

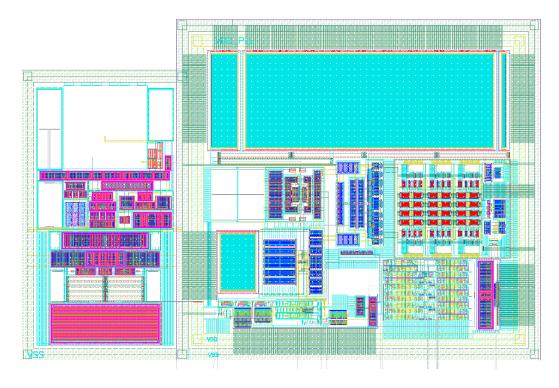

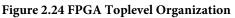

| Figure 2.24 FPGA Toplevel Organization                      |    |

| Figure 2.25 ASIC Toplevel Organization                      |    |

| Figure 3.1 Layer Stack of EXTOLL ASIC                       |    |

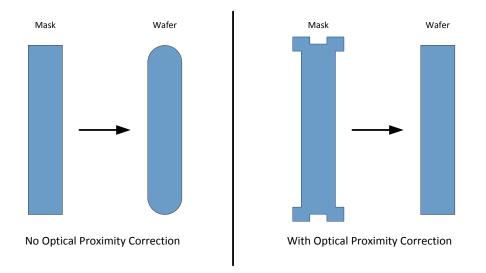

| Figure 3.2 Effect of Optical Proximity Correction           |    |

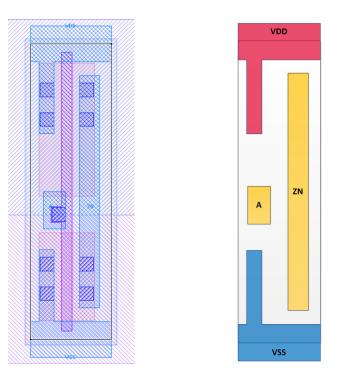

| Figure 3.3 Simple Inverter as Full Layout and Abstract View |    |

| Figure 3.4 EXTOLL ASIC Subversion Structure                 | 53 |

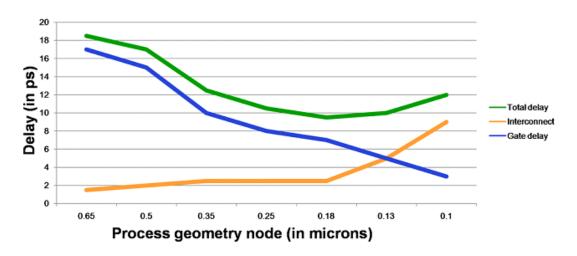

| Figure 3.5 Gate vs. Interconnect Delay                      | 55 |

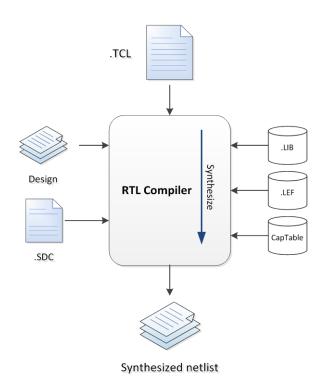

| Figure 3.6 Synthesis Input and Output Files                 | 55 |

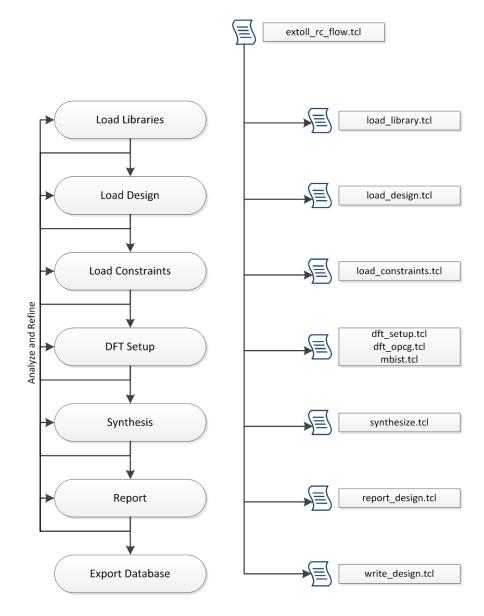

| Figure 3.7 Frontend Flow Organization                       | 57 |

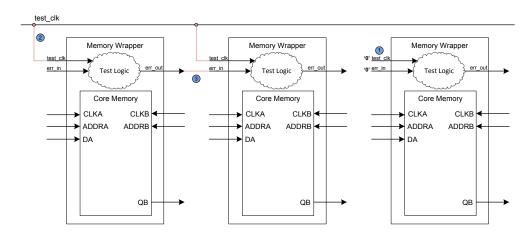

| Figure 3.8 Memory Test Connections                          |    |

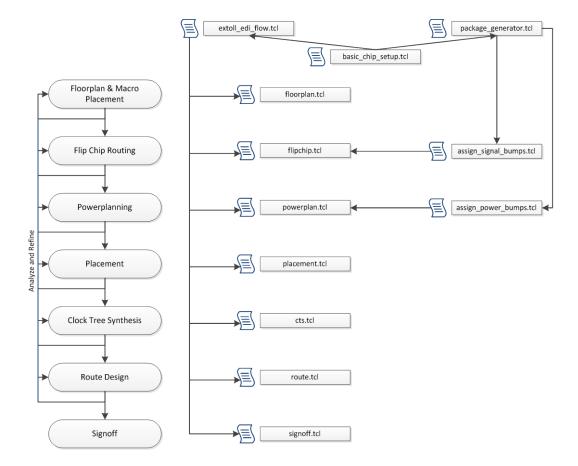

| Figure 3.9 Backend Flow Organization                        | 61 |

| Figure 3.10 Signal Reach in One Clock Cycle (8 FO4)         | 64 |

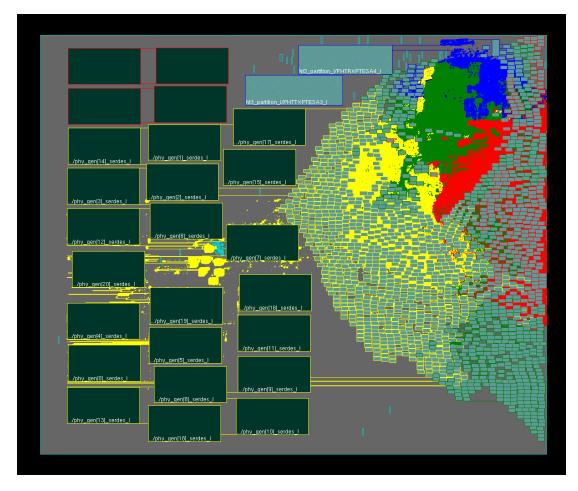

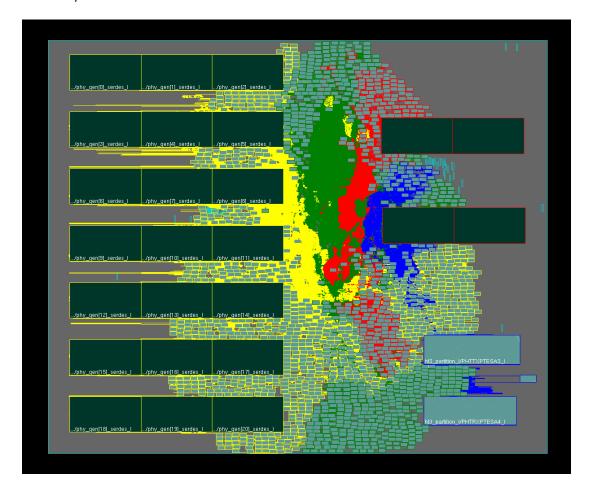

| Figure 3.11 Automatic Placement without Floorplan           | 65 |

| Figure 3.12 Global Datapath Analysis                        | 67 |

| Figure 3.13 Automatic Placement with Preplaced Macros       | 68 |

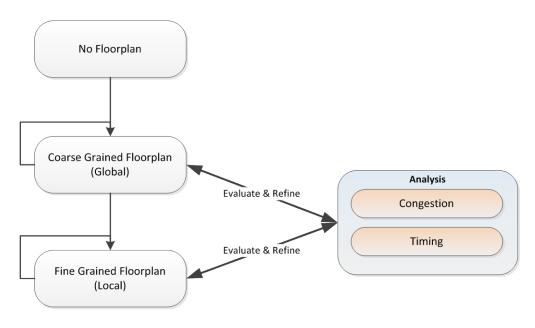

| Figure 3.14 Hierarchical Floorplanning                      | 69 |

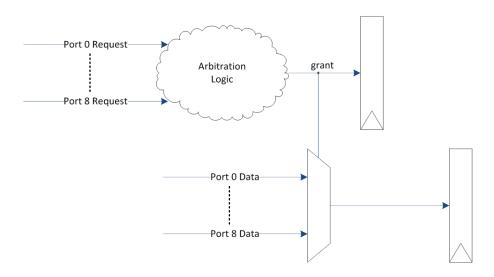

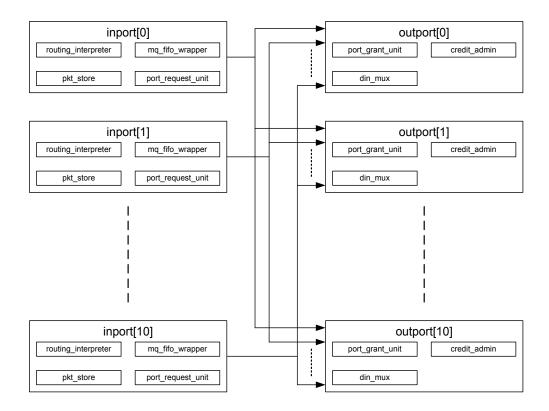

| Figure 3.15 HTAX Structure                                  | 72 |

| Figure 3.16 EXTOLL XBAR Structure                           | 73 |

| Figure 3.17 Relative Placement Example                      | 74 |

| Figure 3.18 Schematic of a 4x2 Register Based RAM           | 76 |

| Figure 4.1 Connectivity Design Constraints                  | 79 |

| Figure 4.2 Schematic Representation of Signal Path          |    |

| Figure 4.3 Samtec HDI6 Connector                            |    |

| Figure 4.4 PCB Layout of HDI6 Connector                     |    |

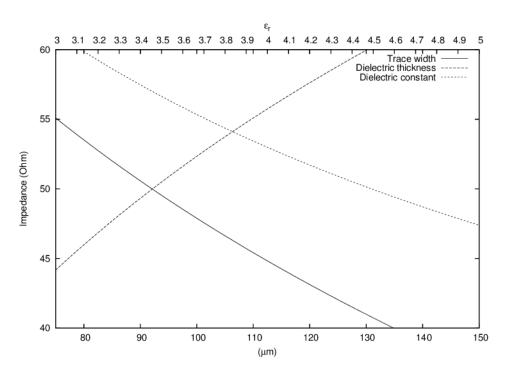

| Figure 4.5 Impact of Parameters on Impedance                |    |

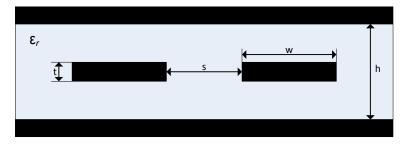

| Figure 4.6 Differential Stripline                   | 84  |

|-----------------------------------------------------|-----|

| Figure 4.7 Example PCB Stackup                      | 85  |

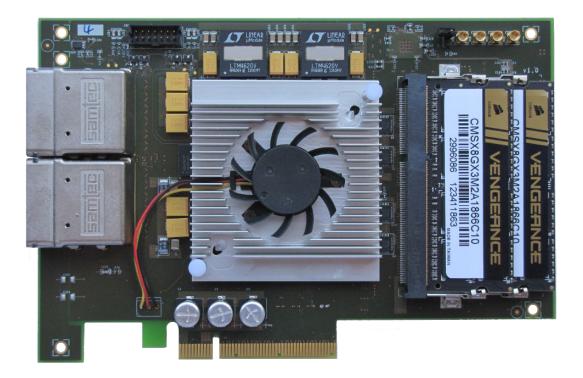

| Figure 4.8 Aspin Test Board                         | 86  |

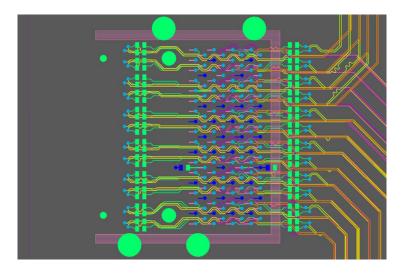

| Figure 4.9 Differential Pair BGA Breakout           | 88  |

| Figure 4.10 A 12x Serdes Breakout                   | 89  |

| Figure 4.11 Scripting Approach                      | 91  |

| Figure 4.12 Single Channel Simulation Setup         | 92  |

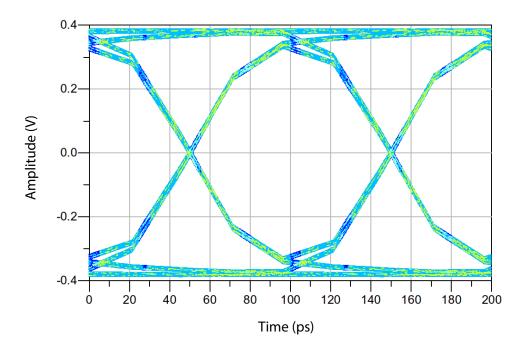

| Figure 4.13 Eye Diagram at 10 Gb/s                  | 93  |

| Figure 4.14 Example of an Insufficient Power Supply | 94  |

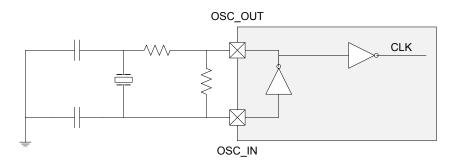

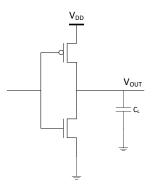

| Figure 4.15 Oscillator Circuit                      | 98  |

| Figure 5.1 Test Options                             | 105 |

| Figure 5.2 Chip Test Flow                           | 106 |

| Figure 5.3 Teradyne Tester                          | 107 |

| Figure 5.4 Microprobe Vx-MP Probe Card              | 107 |

| Figure 5.5 Spring Pin                               | 108 |

| Figure 5.6 Test Cost Analysis                       | 112 |

| Figure 5.7 Scan Chain Structure                     | 114 |

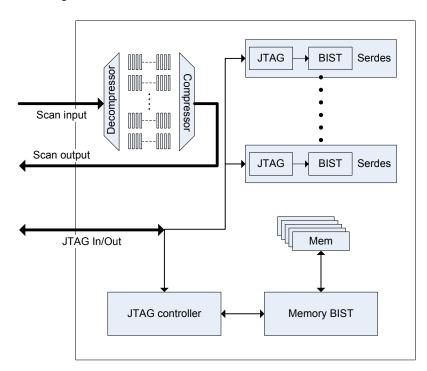

| Figure 5.8 EXTOLL Test Organization                 | 115 |

| Figure 5.9 CMOS Inverter                            | 118 |

| Figure 5.10 Test Data Processing                    | 120 |

| Figure 5.11 Design Space for Tester Development     | 120 |

| Figure 5.12 Test Platform Proposal                  | 122 |

|                                                     |     |

# **List of Tables**

| Table 2.1 Competitor Overview                 | 11  |

|-----------------------------------------------|-----|

| Table 2.2 Timing Parameters and Their Meaning | 18  |

| Table 3.1 Design Data Storage                 | 54  |

| Table 3.2 Floorplan Evaluation                | 70  |

| Table 3.3 XBAR Area Distribution              | 73  |

| Table 4.1 EXTOLL High Speed Connectivity      | 79  |

| Table 4.2 Connector Overview                  | 81  |

| Table 4.3 HyperTransport Interface Pins       | 96  |

| Table 4.4 PCI Express Interface Pins          | 96  |

| Table 4.5 Network Interface Pins              | 97  |

| Table 4.6 Clocking Pins                       | 97  |

| Table 4.7 Configuration and Reset Pins        | 98  |

| Table 4.8 Miscellaneous Pins                  | 99  |

| Table 4.9 JTAG Interface Pins                 | 100 |

| Table 4.10 Dedicated DFT Pins                 | 101 |

| Table 4.11 Digital Core and I/O Supply        | 102 |

| Table 4.12 HyperTransport Supply              | 102 |

| Table 4.13 Clocking Supply                    | 103 |

| Table 4.14 Serializer Supply                  | 103 |

| Table 5.1 Parameters for Die Calculation      | 109 |

| Table 5.2 Parameters for Cost Calculation     | 111 |

## 1 Introduction

## 1.1 Motivation

"I think there is a world market for maybe five computers"

Alleged quote by Thomas Watson, IBM CEO, 1943

Regardless of the historical accuracy of the quote it represents a view that no one could imagine that there is a need for actual computing power. Nevertheless, performance of processors has risen steadily and continues growing exponentially. On the basis of Moore's law that states that the number of transistors in an integrated circuit doubles every two years it was predicted that the performance doubles every 18 months. This prediction has even been surpassed by the supercomputer market.

Figure 1.1 TOP500 Development

### Introduction

A historical observation from the Top500 list<sup>1</sup> [1] in figure 1.1 shows that the maximum performance of the fastest installation which is measured by the Linpack benchmark [2] has increased tenfold about every four years. With the first installation breaching the 10 Petaflop/s barrier in November 2011 it can be projected that the Exascale era will be reached around 2020. However, current architectures will not scale up to this point [3]. One project to meet the Exascale challenge is the DEEP (Dynamic Exascale Entry Platform) project which is supported by the European Union through the Seventh Framework Programme (FP7).

The idea is to combine two separate networks. One is a typical cluster installation (CN) connected through a central InfiniBand switch. The other network is a specialized booster network consisting of accelerators (BN) that are connected in a torus topology through a specialized high-performance, low latency network, EXTOLL. The following figure 1.2 shows the organization of the DEEP architecture and how the two networks are connected through so called Booster Interconnect (BI) nodes.

#### Figure 1.2 DEEP Architecture

The following figure 1.3 shows a schematic representation of a Booster Node. At the moment it is planned that one hardware node will consist of two booster nodes.

$<sup>^{\</sup>rm 1}$  Based on the 39  $^{\rm th}$  list from June 2012

#### Figure 1.3 Booster Node Architecture

The noteworthy feature is that the system does not need a host CPU, the accelerator (Xeon Phi) is directly connected to the network through EXTOLL.

## 1.2 Scope of Work

The International Technology Roadmap for Semiconductors (ITRS) identified "Networking" in their 2011 report [4] as one of the key markets that drives the future of the semiconductor industry. The need for higher bandwidth which is estimated to quadruple every 3-4 years, the short time-to-market, high reliability and the need to keep the power envelope low lead to advances in serializer technology, embedding of switching functionality and the ability to integrate a larger number of gates in a chip to move all system functions into a single large System-on-Chip (SoC). An analysis of the 10 fastest computers in the Top500 list suggests that a custom / proprietary interconnect that is tailored specifically for the system is still the best path to take. Such a custom interconnect that was selected for the DEEP system is the EXTOLL interconnect which was specifically designed for the High Performance Computing (HPC) market. Because it is an integral part of the functionality of the Booster Network as seen in figures 1.2 and 1.3 it is especially important that it will have the highest performance available so that the whole system will perform outstandingly. Highest performance means that EXTOLL must be implemented as an ASIC [5] which allows both a high internal frequency and also fast connectivity to the outside world. This cannot be achieved with an FPGA since the performance gap between FPGAs and ASICs is rather large despite continuous improvements in FPGA technology. For a purely logic based design an ASIC will perform about 4 times faster than an FPGA [6].

However, a system does not only consist of a single component but is a complex ecosystem that represents a pretty wide design space. With an ASIC that is designed from scratch this

## Introduction

ecosystem can be optimized for all components. But this multi-dimensional optimization problem must be solved concurrently since each decision has a direct impact on both the performance and the optimization space of the remaining components.

This thesis analyzes four different aspects of the EXTOLL chip and its surrounding ecosystem and either proposes solutions or methodologies that significantly improve the final results.

### - Design

The key differences between FPGA and ASIC design are worked and out, especially in the area of on-chip memory and an innovative methodology is introduced to handle on-chip error checking and correction in a transparent way.

### - Physical implementation

Special consideration is given to the floorplanning process and how it relates to both physical constraints like signal arrangement and logical constraints like the dataflow inside the design.

### - Connectivity and signal integrity

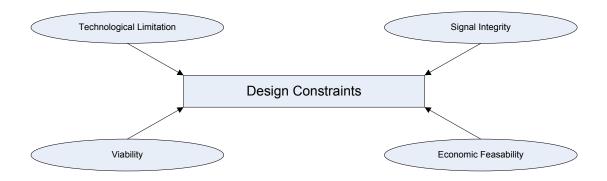

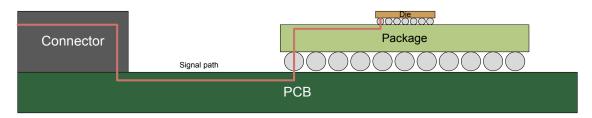

The signal path from the chip, through the package and the PCB to the connector is analyzed and a package definition is proposed that is an optimal solution considering the technological limitations, viability, signal integrity and also cost concerns.

### - Testing

At last a cost model concerning test is developed and as a consequence of this a new test platform is presented that is able to test packaged EXTOLL chips in every aspect.

## 1.3 EXTOLL Design

EXTOLL (EXtended aTOLL) is the successor of ATOLL, the first network chip developed at the Chair of Computer Architecture, University of Mannheim, which was implemented in a 180nm process from UMC [7]. The good performance numbers and many promising ideas lead to the next research project EXTOLL which has been in development for the last years.

EXTOLL can be logically divided into three different parts:

- The host interface part, which contains two exclusive commodity host interface controllers

- The EXTOLL core logic part, which contains both the FUs (functional units) that make up EXTOLL's basic functionality and assisting units that are needed to support all features of EXTOLL

- The network interface part which includes the switching functionality as well as the control logic to interface to the outside world

The block diagram in figure 1.4 gives an overview of the design blocks inside EXTOLL that will be shortly described in the following.

#### Figure 1.4 EXTOLL Block Diagram

## 1.3.1 Host Interface

One of the supported host interfaces is HyperTransport (HT) [8] that is specific to AMD based systems. The *HT3 core* [9] inside of EXTOLL is a standard compliant implementation of the protocol supporting all required features to directly connect to modern AMD processors. The HT3 core is connected to the *HT PHY* that takes care of the physical layer implementation of the HT links similar to the PHY implementations in the CPU [10] [11]. With a link width of 16 bit and supported transfer rates of up to 2.6 GT/s the link is able to sustain a raw bandwidth of 10.8 GB/s.

Besides HyperTransport EXTOLL also supports PCI Express (PCIe) [12] as a host interface. Both the *PCIe PHY* that handles the physical layer and the *PCIe core* that implements the

## Introduction

data link layer and transaction layer are external IP and are not developed in-house. They both support the latest 3.0 revision of the specification, thus providing up to 16 GB/s link bandwidth for an x16 connection to the host system. The PCIe core can be configured either as an endpoint, thereby assuming the role of a traditional network interface controller (NIC), and also as a rootport. Working as a rootport allows a direct host-independent communication with an endpoint, e.g. a graphics card. Therefore an arbitrary device can be added to the network without the need for a host CPU. Although HyperTransport and PCIe share architectural similarities they are not directly interchangeable. Thus, a translation layer, the *PCIe Bridge* [13], is needed to generate packets that can be understood by the following modules and to handle the peculiarities of the PCIe core and protocol.

The *HTAX Bridge* [14] is the interface between the host interfaces and the internal EXTOLL logic. In RX direction it translates the packet format of the IP cores to the HTOC protocol that is used internally for communication between functional units. For transmitting packets the translation is reversed.

*HTAX* [15] is an internal 9x9 on-chip crossbar that connects the three virtual channels of the host interfaces to the functional units inside EXTOLL. It represents a protocol independent switching architecture with low overhead for direct communication between two ports.

## 1.3.2 EXTOLL Core Logic

The *VELO* (Virtualized Engine for Low Overhead) [16] functional unit has been designed to transmit small messages up to a size of 64 bytes (which corresponds to one cache line in today's x86 based processors) efficiently and with minimal overhead. On an FPGA prototype sub µs latency could be achieved with minimum size packets. Nevertheless, VELO can also transmit larger messages, however, its efficiency decreases the larger the packets get.

For larger bulk transfers the *RMA* (Remote Memory Access) [17] unit was introduced. It provides put and get operations that can be started with a single packet from the host system and then work independently of the processor. It can work with both physical and virtual addresses. Both VELO and RMA are fully virtualized and therefore allow concurrent access from different user space processes.

The ATU (Address Translation Unit) [18] is a supporting unit for the RMA and provides address translations from virtual addresses that are used in RMA to physical system addresses without involving the operating system and therefore without the kernel overhead that would be required otherwise. Essentially it can be viewed as an MMU (Memory Management Unit) since it performs a comparable task to the MMU in a CPU.

The *SMFU* (Shared Memory Functional Unit) [19] introduces support for a non-coherent distributed shared memory by forwarding local stores and loads to non-local nodes. This is done by splitting the local CPU's address space in local and remote memory. Loads and stores that are mapped to remote memory will be handled by the SMFU and transferred to the correct node and executed there without any additional software support.

The *RF* (Registerfile) [18] module contains control information for all internal units and is also used to collect debug data that is generated in the various instances. Since it is mapped into the system's address space the values can be easily changed through the system software. The register file is automatically generated from an XML specification which leads not only to a RTL implementation but also code for kernel drivers, documentation and verification is generated automatically. With tens of thousands lines of codes and more than thousand internal registers it is an integral part of EXTOLL. Because the register file is organized in a hierarchical way register file nodes can be distributed over the chip and move into functional units to shorten signal paths between the register file and the unit that is controlled by it.

The *SNQ* (System Notification Queue) [18] serves two purposes. It is used to send interrupts to notify the host system that an important event has occurred in the device that should be handled by the kernel driver. The second purpose is to collect debug information upon triggers from units in the design and dump the information to main memory.

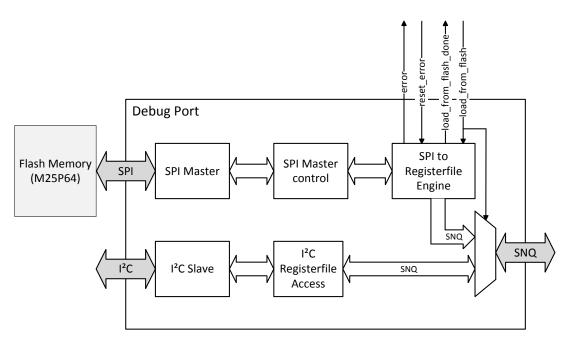

The *Debugport* [20] is actually not a part of the EXTOLL functionality but a safeguard against mistakes in the design phase that might be discovered after the chip is produced and brought up in the lab. It is also, as the name implies a method to access debug information after the host system has crashed and software access to the device is no longer possible. In order to perform this functionality the module contains two external interfaces. The Debugport connects to an SPI flash that can contain replacement values for registers in the register file. Those values will be loaded into the chip before the internal reset is released so that they are available at the startup of the logic. By creating this bypass it is possible to correct wrong initialization values for the host interface, for example, that might keep the chip from being recognized in the system. In order to load debug values from the register file without access to the system the Debugport also contains an I<sup>2</sup>C slave that is able to access the complete register file. The module shares a direct access path to the register file with the SNQ so that it does not have to depend on a clean state in the rest of the system.

## Introduction

The *NP* (Network Port) [14] is the interface between the functional units and the EXTOLL NIC. Since the functional units are not aware of protocol details the required framing and deframing is performed in the NP as well as the flow control required for the network.

## 1.3.3 EXTOLL NIC

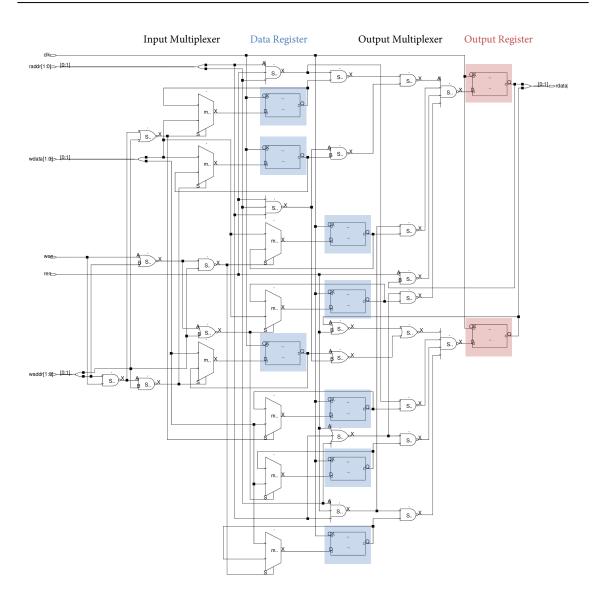

The key element of the EXTOLL NIC is the internal 11x11 *EXTOLL XBAR* [14]. The routing is performed on a table-based algorithm [21] which makes it easy to implement adaptive routing and reroute packets in error situations. Since switching is done using VCT (Virtual Cut Through) the crossbar has significant memory requirements. With a route-through latency of 17 clock cycles it shows an excellent performance.

The *LP* (Link Port) [22] protects EXTOLL packets by adding a CRC to them. In the case of an erroneous transmission the packet is marked and a retransmission is started. Therefore the LP contains a retransmission buffer that is able to store at least as many packets as are required to perform a retransmission from the point when the defective packet was sent.

The *Link Control* units are the interface between the logical packets in the link port and the physical transmission in the PHY layer. Like earlier FPGA based versions the EXTOLL ASIC uses 8b10b coding to ensure DC balanced transmission. The Link Control module also contains logic for link initialization, rate switching and training.

## 1.4 Outline

This thesis can be divided into two parts. Chapter 2 and 3 focus on the EXTOLL ASIC and its implementation while the subsequent chapters 4 and 5 deal with the ecosystem around EXTOLL. Each chapter focuses on one key aspect in the design that was analyzed and optimized during the design process.

Chapter 2 gives an overview of the technological obstacles during the planning phase of the EXTOLL chip. It also shows the relevant changes from an earlier FPGA based implementation to an ASIC based implementation and focuses on the technological differences. Some modules that were specifically designed for the ASIC implementation are also introduced.

Chapter 3 introduces a modern ASIC flow that is used to implement the EXTOLL chip. It gives a short overview of the complete design flow starting with synthesis up to the final tapeout for chip production. A set of guidelines are presented for collaborative work on such

a large chip. The rest of the chapter focuses on the development and optimization of the floorplan with respect to the package layout developed in the next chapter.

Chapter 4 analyzes the design space for the package and PCB development for EXTOLL and introduces a suitable solution while keeping signal integrity, production cost and other relevant factors in mind.

At last, chapter 5 focuses on the testing of the EXTOLL ASIC for defects. It describes the challenges in wafer testing and analyzes the cost structure of a complete chip test process. In the end a test environment is presented that is able to perform these tasks in a lab environment.

The thesis is concluded by a last chapter that summarizes the results that were worked out in this thesis. It also reviews the design process and its complexity and introduces a set of guidelines that were learned throughout the development. Finally, it also gives an outlook to future developments regarding EXTOLL.

# 2 EXTOLL ASIC

## 2.1 Design Decisions

The EXTOLL research project has been started as a successor of the ATOLL interconnect, the previous interconnection network of the Computer Architecture Group at the University of Mannheim. After the first version of EXTOLL (R1) was able to confirm and supersede [23] the competitive results of ATOLL and more features were introduced to distinguish the network from other vendors it was decided to move EXTOLL from a sole research interest to a real product to be introduced to the global HPC market. Although ATOLL was built as an ASIC, subsequent development switched to FPGAs that could be utilized easily as a rapid prototyping platform. The idea to commercialize EXTOLL had to lead to a review of design alternatives in order to determine the best path to create a product with a profitable price structure and competitive performance.

## 2.1.1 Performance Comparison

| Product    | Technology | Clock<br>Frequency | Link<br>Bandwidth | Latency | Msg rate    |

|------------|------------|--------------------|-------------------|---------|-------------|

| Infiniband | ASIC       | ~500 MHz           | 40 Gb/s           | 1.59 μs | 6.7m msg/s  |

| QDR        |            |                    |                   |         |             |

| 10GE       | ASIC       | ~125-312           | 12.5 Gb/s         | 12.5 µs | <2.5m msg/s |

|            |            | MHz                |                   |         |             |

| Cray       | ASIC       | 650 / 800 MHz      | 75 Gb/s           | 1.5 µs  | ~2m msg/s   |

| Gemini     |            |                    |                   |         |             |

| Tianhe-1a  | ASIC       | unknown            | 80 Gb/s           | 2.5 µs  | 1-3m msg/s  |

| TOFU       | ASIC       | 312.5 MHz          | 50 Gb/s           | 1.5 µs  | >8m msg/s   |

| Ventoux    | FPGA       | 200 MHz            | 16 Gb/s           | 1.2 µs  | 25m msg/s   |

| (EXTOLL)   |            |                    |                   |         |             |

In order to define the minimum performance parameters that EXTOLL had to achieve a look at the competitors at that time was necessary:

#### **Table 2.1 Competitor Overview**

Three characteristics can be used to qualify the performance of an interconnection network:

### - Latency

The latency describes how much time it takes to send the smallest possible packet between two communication partners. Unlike the round-trip latency this measurement excludes the time that is spent processing the packet in the receiver and is therefore more accurate.

## - Link bandwidth

The link bandwidth defines the raw speed of a link between two endpoints including the protocol overhead. This is an important metric for bulk transfers since best utilization is usually reached by using maximum sized messages to carry the data

### - Message rate

The last important characteristic is the message rate. It defines how many messages can be exchanged between two endpoints in a second. Obviously, the highest message rate can be achieved by using minimum sized packets.

Naturally, all these parameters are interlinked in some way and an overall outstanding performance can only be reached by tuning each characteristic. Nevertheless, some applications will benefit more from improving one metric over another because of their unique communication patterns. All these measurements can be determined by a set of micro benchmarks from Ohio State University, the OSU Micro-Benchmarks suite [24].

It is clearly visible from the table that the Ventoux prototype is comparable in terms of startup latency and even surpasses competitors regarding the message rate. The notable exception is the raw link bandwidth which is the second worst of all compared technologies. It is obvious that this is the area in which a commercial product must step up a notch in order to provide unique performance across all metrics. Of course, it is not unfavorable if the other numbers also improve by switching to another technology.

## 2.1.2 Technology Analysis

There are some limitations you have to consider when comparing to an industrial project, especially with regards to development costs. Since EXTOLL stemmed from a research project it was not required to develop the design from scratch. However, the high costs associated with modern semiconductor technology prevent both complete pre-development in a research context and also personal funding. This means that external funding must be acquired from investors or venture capitalists. Unfortunately, this is rather difficult in Germany where investors prefer spending their money on software projects. It is unusual to acquire substantial sums for a hardware project because of the high risk involved. This also

means that the budget for a chip implementation is limited and it is important to earn money as soon as possible in order to keep the business going.

The following design space diagram in figure 2.1 outlines the different paths that can be taken in order to realize a commercial EXTOLL product.

Figure 2.1 Design Space Diagram for EXTOLL Technology Selection

FPGA's logic density has steadily increased from generation to generation. Altera's Stratix V family contains devices with up to 950k equivalent logic elements while Xilinx's biggest Virtex-7 device even offers two million logic cells. Although these numbers are not exactly comparable because of different internal structures they both show that FPGAs provide an enormous amount of logic resources. As a comparison, the EXTOLL Ventoux prototype implemented on a Virtex-6, albeit with a slightly lower logic complexity, fills up a device with 240k logic cells. Thus, it can be assumed that an implementation of all the logic inside a single FPGA would be feasible. However, prices from an authorized distributor for the largest Virtex-7 available are in the range of \$30,000 per device<sup>2</sup>. Although Xilinx offers significant discounts for larger volumes [25], the final unit price would probably still be more than \$1,000. Coupled with the fact that it is very hard to exceed internal clock frequencies of 200 MHz (as seen in the prototypes) for complex logic it is easily transparent that it is not possible to build a product that is competitive in both performance and financial aspects.

Both Altera and Xilinx as major FPGA vendors also offer solutions for hardened FPGAs. However, their approaches are fundamentally different. Xilinx takes FPGAs that are not 100% functional and checks if the defective area affects the customer's design. If the design does work correctly this chip is sold as an EasyPath device. Since the chips are basically the same devices as the original FPGAs they offer the same features as before but their performance will not increase. The only advantages of this approach are the quick turn-

<sup>&</sup>lt;sup>2</sup> Avnet price list, checked in 09/2012

around time and a price reduction of about 30% per device [25]. Altera's HardCopy devices on the other hand are custom produced devices. They contain configurable logic elements as basic building blocks similar to the structure of an FPGA as well as the custom IP that is also available in FPGAs like PCIe macros, however, the chips are fabricated by creating masks for the upper metal layers that contain the wiring between the logic blocks. Since the lower metal layers in a custom chip that contain the structures with the finest pitch and therefore are the most expensive masks in an ASIC design are fixed the customer only has to pay for the metal layers required for wiring. Because these structured ASICs are completely different chips than the FPGAs they must be requalified for correct functionality. In contrary to Xilinx's solution HardCopy chips offer an increased performance of up to 50% and a significant power reduction [26]. Altera also promises a price reduction of about 80% per unit compared to a similar FPGA without taking into account the higher NRE costs for the masks. Though a performance improvement is achievable the results do not justify the higher investment.

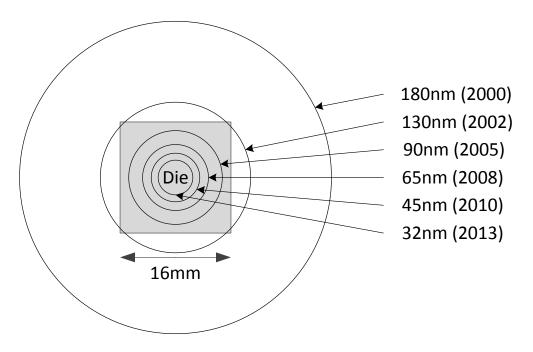

The most versatile solution is the production of a custom ASIC. This gives the most flexibility with regards to features that can be incorporated into the chip. A short look at the competitor overview in table 2.1 shows that the certain way to reach acceptable performance is the implementation in an ASIC. However, in comparison to FPGA solutions ASICs suffer from high initial NRE costs:

- Mask costs

All masks for the ASIC production must be fully paid by the customer. A full mask set will cost hundreds of thousands of dollars even for relatively mature technologies like 90nm. One can say, that the mask costs for each step to a smaller process node will roughly double which sets a full set for 28nm in the range of several million dollars.

- EDA tools

While FPGA vendors sell their tools for a moderate price of less than \$10,000 for dozens of licenses or even give the tools away for free designers that want to implement an ASIC need a whole set of tools for the different steps in the design flow and must pay prices that are an order of magnitude higher for a single license.

#### - IP costs

A large number of IP elements (either Soft IP like PCI Express cores or Hard IP like serializers, PLL and memories) that come for free with FPGAs must be purchased for an ASIC development. Although foundries like TSMC usually offer a basic functionality like standard cell libraries, simple CMOS I/O libraries and sometimes

memory compilers for free it might be important to buy these elements also from 3<sup>rd</sup> party vendors if the performance of the free cells does not match the requirements. Depending on the complexity of the IP and the technology node prices range from tens of thousands of dollars up to more than a million dollars per IP license.

Altogether, the initial investment is rather high and exceeds the volume of one million dollars without problems. Despite these circumstances the price per unit is relatively cheap. Depending on the chip size which determines how many chips can be cut out of a wafer a price of less than \$100 per die is undoubtedly achievable.

Since IP costs and EDA tool prices do not change much throughout process nodes the differentiating cost factor are the mask costs. Therefore the correct technology is a combination of technological feasibility (e.g. required performance, IP availability), existing investment and expected revenue.

With a prospective volume of about 25k units over the lifetime of EXTOLL it is very important to keep the costs as low as possible. An investment in 28nm, for example, would lead to a tremendous unit price (especially regarding the rumored low yield) which will move the point of ROI to the end-of-life of EXTOLL which means that no profit can be reached at all.

Because of the low volume, a MLM (multi-layer mask) mask set [27] is a good way to cut costs. For an MLM four layers are combined into one reticle, thus reducing the largest possible die size to one quarter of a reticle. This allows a reduction of the mask costs because fewer masks are needed in total. However, the price of the wafer goes up because it needs more time to be processed due to the additional time required on the wafer stepper. However, for low volume production the mask cost savings exceed the extra cost of the wafer.

For the design a couple of external IP is needed:

- SERDES

An overview of serializers that are able to support PCIe Gen3 [28] shows that no IP is available for 90nm which eliminates this option. Designing Gen3 IP at mature nodes seems to be technologically difficult (or unprofitable) because only few providers offer such IP, most offerings for PCIe Gen3 are available at 28nm. Many vendors skipped the 65nm and 40nm process nodes and designed directly for 28nm.

## - Standard cells

Trial synthesis runs at 65nm showed that the technology is able to support the target frequency of 750 MHz without changes to the RTL (like adding additional pipeline stages). Because 90nm was already out of the question because of the missing serializers it was no longer considered for evaluation. Since 65nm already meets the performance goals smaller nodes will only increase the available margin for increasing the internal clock frequency.

### - HT3 PHY

The PHY that provides the physical layer for the HT3 core is only available in 65nm and was originally developed by ATI. After AMD had purchased ATI the PHY was donated for use. However, HyperTransport targets only a niche market since AMD continuously lost market shares in the server market over the last few years. Thus, the availability of an HT PHY is no key factor for the final decision.

- PLL

A PLL was already available for 65nm from a former research project. A design for other nodes would be possible, the expected performance can be reached in all nodes.

- I/O cells

CMOS I/O cells are provided by the foundry and do not have to be purchased. Special purpose I/O cells that are required for differential signaling must be either purchased or developed. However, there is no special performance criteria for these cells so that they can be obtained for all technology nodes.

- Memory

Memories are usually the factor that limits the design speed in a digital design. As before, it was determined by evaluation that the required performance could be reached by using 65nm. Similar to standard cells, smaller process nodes will only improve the speed and increase the margin for running at higher frequencies.

In the end it was decided to design EXTOLL as a 65nm chip because the combination of IP availability, mask costs and expected revenue was the most compelling of all alternatives while also maintaining the performance goals that are needed to outperform the competition.

Consequently, the following subsections will present the challenges and design guidelines for a successful port from an FPGA based prototype to an ASIC solution.

## 2.2 Transition from FPGA to ASIC

EXTOLL is developed by using the Verilog Hardware Description language [29]. The source files consist of more than 280,000 lines of code that utilize roughly 13MB of disk space<sup>3</sup>. In general Verilog is target platform agnostic and will only be mapped during synthesis to a target technology. However, there are certain aspects that need to be handled in a different way depending on the final implementation.

Due to the size of the code base it is not feasible to maintain a completely separate development environment. Instead it is important to keep as much code as possible unmodified and shareable across all platforms.

Nevertheless, there are some constructs that will have to be developed separately while keeping in mind that the overall structure of the design should not be modified.

The following aspects have been identified for special consideration:

- Internal memory, i.e. how the embedded memory is generated, accessed in the chip and how it is protected

- Clocking / Timing, i.e. how are the clocks generated

- Reset, i.e. how is reset generated and distributed

- Testing, i.e. is a special testing methodology required

- Toplevel, i.e. how are the modules connected together

These issues will be addressed in the following paragraphs and guidelines for a successful transition will be worked out.

## 2.3 Design Guidelines

The beginning of the design phase is the place where most impact can be made on the performance of the chip. RTL that was badly implemented will hinder the overall performance and can even waste runtime because tools are forced to optimize sections of code that will have a hard time reaching timing closure or might even fail timing. An old saying in computer science, "garbage in, garbage out", is also valid for hardware design. Therefore it is important to take care already in the beginning of the design process.

<sup>&</sup>lt;sup>3</sup> Values determined in Oct.'12, excluding external PCIe core

## 2.3.1 Timing Basics

Flip-flops have a set of timing parameters that must be observed so that the flip-flop is not in danger of becoming metastable. The following table 2.2 and figure 2.2 give an overview of the different timing parameters for a flip-flop that is triggered on the positive clock edge.

| Abbr.            | Timing parameter     | Description                                                |

|------------------|----------------------|------------------------------------------------------------|

| t <sub>su</sub>  | Setup time           | The time that the new value on the D input must be stable  |

|                  |                      | before the rising clock edge                               |

| t <sub>hd</sub>  | Hold time            | The time that the value on the D input must be kept stable |

|                  |                      | after the rising clock edge                                |

| t <sub>co</sub>  | Clock-to-output time | The time between the sampling of the new value on the D    |

|                  |                      | input and its subsequent appearance on the Q output        |

| t <sub>rec</sub> | Recovery time        | Consistent to the setup time, but related to asynchronous  |

|                  |                      | inputs (i.e. reset)                                        |

| t <sub>rem</sub> | Removal time         | Consistent to the hold time, but related to asynchronous   |

|                  |                      | inputs (i.e. reset)                                        |

Table 2.2 Timing Parameters and Their Meaning

Figure 2.2 Flip-Flop Timing Parameters

These parameters also have an influence on the logic that follows afterwards and the performance that can be reached. Setup time violations can be fixed by reducing the propagation delay of the combinatorial logic before the flip-flop (either by upsizing cells or rewriting RTL) or decreasing the internal clock frequency. Hold time violations are independent from the clock and can only be fixed by buffer insertion or cell downsizing and will lead to a non-functional chip if they are not corrected before tapeout.

For the setup time the following formula is valid where  $t_{clk}$  is the clock cycle time and  $t_{pd}$  is the propagation delay of the logic between two flip-flops.

$$t_{clk} \ge t_{co} + t_{pd} + t_{su}$$

Equally, the hold time is defined by the following formula:

$$t_{co} + t_{pd} \ge t_{hd}$$

#### 2.3.2 Reset

A global reset signal is used to initialize a design to a well-known state. However, FPGAs employ a completely different reset strategy than ASICs. FPGAs load their configuration from an external bitstream which means that everything in an FPGA has a predefined initial value so that a reset is actually not required [30]. Nevertheless, the internal registers inside the FPGA support both asynchronous and synchronous reset styles. Analysis show that a completely synchronous reset results in a better timing, an observation that is also indicated by Xilinx [31]. Therefore, the EXTOLL FPGA prototypes use synchronous resets throughout the complete design.

ASICs in return must be reset so that all registers have an initial state. Synchronous resets suffer from two disadvantages. They require a stable clock because the reset signal is only sampled at a clock edge and the reset pulse must be at least one cycle long so that it can be detected. Therefore ASICs are usually reset asynchronously. However, this introduces the problem of reset removal as characterized in the previous section 2.3.1.

A well known solution is the reset synchronizer circuit [32][33] showed in the following figure 2.3.

Figure 2.3 Reset Synchronizer Circuit

This simple circuit leads to an asynchronous assertion of the reset signal because the Q output of the second flip-flop (the final reset signal) will go to 0 immediately as soon as the *ARES\_N* signal switches to 0. In the case of reset deassertion the value 1 of the first flip-flops D input will be propagated through the two stages. Only the first flip-flop in the synchronizer is in danger of becoming meta-stable because the removal time might be violated. However, the second flip-flop will sample a valid input in the first cycle. In the second cycle the input will be stable again and once again a valid input will be sampled. Thus, the second flip-flop cannot become meta-stable and an invalid state will not be propagated along the reset tree.

Because of the arbitrary reset styles all *always* blocks have two sets of sensitivity lists that are distinguished by a global *ifdef* macro. One set will lead to a synchronous reset style for an FPGA implementation the other will infer an asynchronous reset for an ASIC.

In general it is important not to confuse a reset signal with an init signal to set the logic back to a known state sometime during operation. Reset should only be used directly after powerup to avoid unknown states. If it is necessary to "reset" the logic later on this functionality should be introduced into the synchronous logic path. Adding combinatorial logic to the reset path will only lead to problems later on during construction of the reset tree in the backend design process. It might also introduce the problem of a reset glitch because the output of a combinatorial cell might change its state for a short time (i.e. it glitches) whenever an input changes even though the change on the input will not lead to another output. In this case the following logic might be reset unintentionally.

There is also a pitfall with the Verilog implementation if registers are used inside the logic although they are not resetted explicitly. This will cause the synthesis tool not to treat reset as an ideal net but like any other net in a synchronous design. The condition for the non-reset case (that is present in the code) will be combined with the logic that feeds the register. This leads to a highly buffered reset net and completely ruins the timing for that path.

## 2.4 Embedded Memory

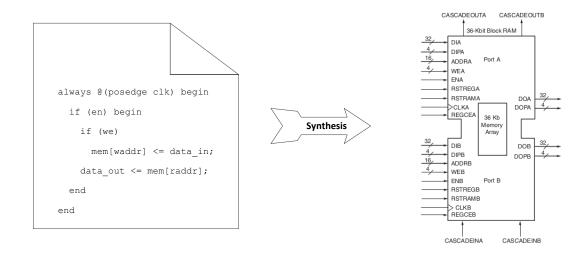

In FPGAs using memory is very easy. All proprietary synthesis tools from either one of the major FPGA vendors or 3<sup>rd</sup> parties like Synopsys recognize simple Verilog language constructs and are able to map them to the integrated memory blocks [34] available in the FPGA. This flow is depicted in the following figure 2.4.

Figure 2.4 FPGA Memory Flow

In ASICs, however, memories are usually generated with a memory generator, a special purpose tool that builds the memory already as an optimized structure for the target technology. The designer must instantiate this customized block in the design to use it. This gives less flexibility in terms of configuration.

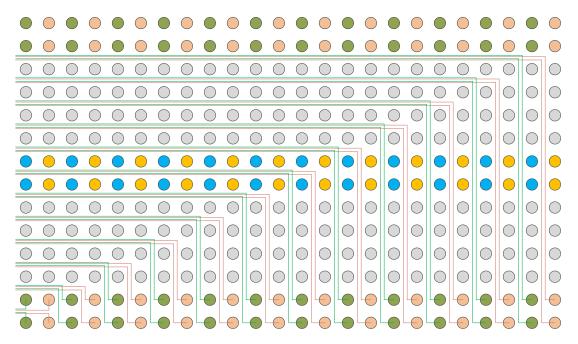

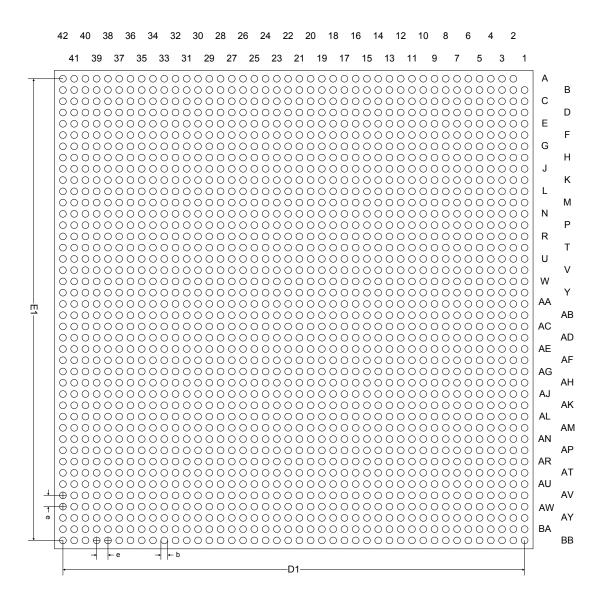

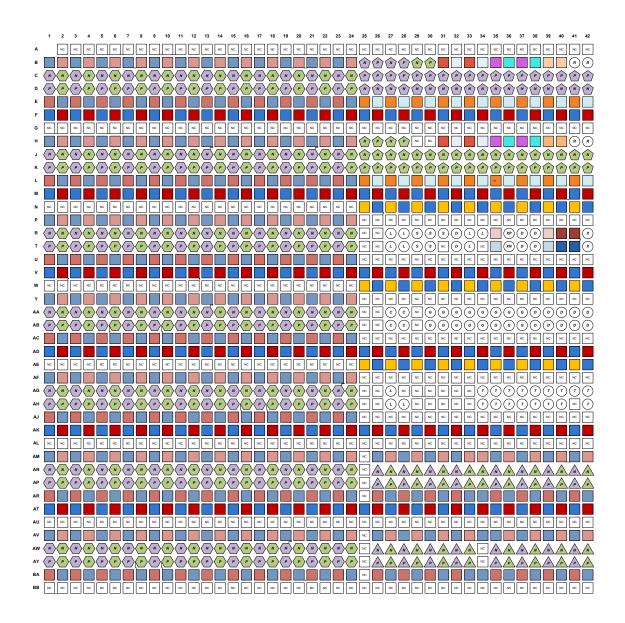

EXTOLL consists of about eighty different RAM configurations, ranging from small sizes like 16x61 up to really large memory sizes like 4096x64. Although it is possible to generate RAM macro blocks for each of these configurations this would result in a large amount of libraries that only differ marginally with respect to area and speed and increase the load time and the memory consumption of the EDA tools.

Therefore the best approach is to generate a small number of building blocks in typical configurations and build up all other configurations out of these building blocks. Although this will waste area for RAMs that cannot be matched exactly to these blocks the easier handling outweighs that disadvantage by far. For area critical designs this conclusion is probably not valid, the EXTOLL die, however, will have enough space so that resource saving

is not necessary. Constraining the designer to use only a small set of memory sizes as an alternative only limits the flexibility in handling RAMs. It makes portability more difficult since the basic RAM block size of an FPGA is not very efficient for an ASIC due to its small capacity.

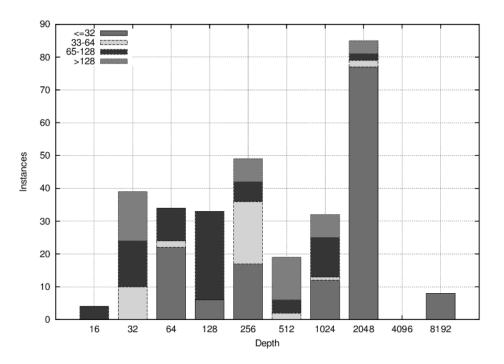

The following figure 2.5 shows the distribution of memory sizes that are required. For simplicity the widths are divided in bins of powers of two. Several observations can be made from the chart:

- There are a large number of RAMs with widths of less than or equal 32 bits that have many entries though. Altogether almost 100 instances can be found.

- Combining the first four columns will add up to another 100 instances. Most of these instances are wider than 64 bits.

- Most of the RAMs with a depth of 256 entries are less than 64 bits wide.

- Instances with widths of more than 128 bits are relatively uncommon.

Since the internal datapath has a width of 128 bits it is evident that there will also be many instances required that have the same data width. Many modules employ at least one FIFO to store internal data before it is forwarded to the next unit.

Figure 2.5 Memory Size Distribution

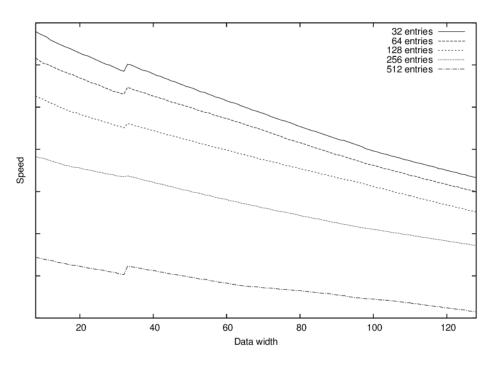

An analysis of the speed of the memories which is shown in the following figure 2.6 (y-axis is unlabeled to hide proprietary data) shows that the speed decreases in a linear way if the RAM becomes wider. It also shows that the starting speed for the least wide configuration decreases with an increasing number of entries. While the distance between the three smallest configurations is almost the same, the offset becomes higher as soon as 128 entries are exceeded. Although all configurations are nominally faster than the required internal clock speed of EXTOLL the margin between that frequency and a RAM with 256 or more entries might become critical so that there might be problems getting timing closure.

Figure 2.6 Memory Speed Analysis

#### 2.4.1 Memory Faults

Memories are more susceptible to defects than standard logic cells because of their optimized, highly packed structure. Memory cells are designed with minimum geometry devices in order to achieve a high memory size / area ratio. Of course, this also means that the probability of a memory fault rises as more and more memories get added to a chip design.

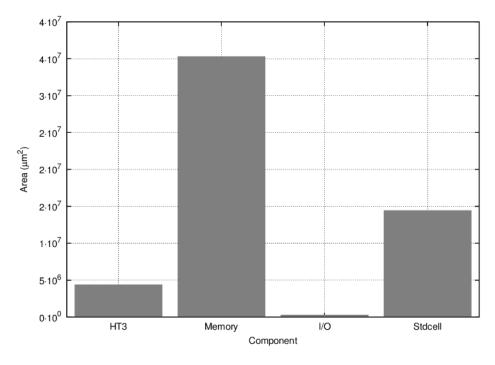

As seen in the following figure 2.7 memories take up a large amount of the occupied chip area in EXTOLL. Therefore it is essential that the possibility of a memory fault must be taken into account and handled in a transparent way.

Figure 2.7 Occupied Chip Area

Memory faults can be classified in dynamic and static faults. Permanent faults are caused by manufacturing errors and can appear with many different fault models. While faults in the address decoder might make some rows or columns in the memory array inaccessible, faults in the array itself might exhibit diverse effects. For example, the cell could be stuck at either 0 or 1 (so called stuck-at faults), it could loose its value (data retention fault) or it might be influenced by the activity of surrounding cells (coupling fault). These faults can be discovered by running BIST (built-in self test) algorithms on the memory [35] which then leads to a removal of the device from the production lot.

Transient or intermittent faults, so called soft errors, are usually caused by external influences like radiation particles and can cause one or more cells to flip their value.

Both types of faults are well known and can be handled by introducing redundancy. Introducing spare rows or columns [36] is a favored way for handling manufacturing defects. If a row or column is identified as defective during BIST all accesses are remapped to the redundant cells inside the memory. The mapping itself is not done dynamically at each startup, instead the reconfiguration is permanently stored in the memory by using electrical fuses. If a process is known to have a bad yield this is a great way to get a larger number of fully functional chips from a wafer, however, the mapping and the additional logic inside the

RAM block leads to a significant degradation of the RAM's performance that can be in the range of several hundred MHz.

Transient faults can be handled by introducing logical redundancy for on-the-fly error checking and correction (ECC). The complexity of this operation depends on the failure rate that must be covered by it. Regardless of the selected algorithm there will be a penalty on the timing of the RAM and additional area consumption. A small side effect is that the probability of a fault is slightly higher because the size of the RAM will also have to increase in order to store the redundancy information. A study [37] by Intel suggests that 75% of all defects can be corrected by using a SECDED (Single Error Correction, Double Error Detection) algorithm while upgrading the error correction to DECTED (Double Error Correction, Triple Error Detection) will improve this rate only marginally by 2% with the drawback of a more complex implementation. A similar conclusion can be found in an analysis in which RAMs are exposed to heavy ion radiation [38]. With a low dosage (which is the most applicable scenario for normal operation) single bit upsets dominate the evaluation of encountered bit errors. The same paper also compares the complexity of SECDED and DECTED algorithms with the conclusion that the encoder complexity is almost the same for a SECDED and DEC algorithm, the decoder, however, suffers from a performance decrease of about 50% for a DEC algorithm in comparison to a SECDED implementation. A complete DECTED implementation even takes up to three times longer. With these results in mind a SECDED algorithm is the best solution for EXTOLL.

Because multi-bit error correction is not required, suitable codes like BCH (Bose-Chaudhuri-Hocquenghem) [39][40] or Reed-Solomon [41] are not needed. Instead a simple Hamming code [42] or an improved version SECDED algorithm, the Hsiao code [43] is used to handle single bit upsets.

Depending on the number of available parity bits m a message with a length of  $2^m - m - 1$  bits can be protected from single bit errors. In order to distinguish between a single bit error that is correctable and an uncorrectable double bit error an additional parity bit is required. Thus, a SECDED implementation requires a Hamming distance of 4.

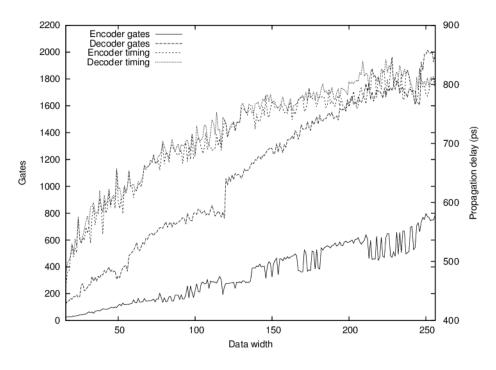

The following figure 2.8 shows the number of gates required in relation to the usable data in a memory as well as the propagation delay through this ECC circuit. As expected, timing becomes worse for larger data widths. Both encoder and decoder roughly take the same time to perform their task so that the penalty is the same for reading and writing to a memory. In contrast the required area for the encoder does not increase as much as the area of the

decoder for higher data widths. For the highest data width that was analyzed the decoder consumes about three times the area of the encoder.

Figure 2.8 ECC Complexity Analysis

As a conclusion it can be said that adding an error correction algorithm that can handle single bit upsets is essential for reliable operation if RAMs are required in a design. Depending on the manufacturing error a SECDED implementation might also give the possibility to reuse chips that would have been marked as defective otherwise, albeit with losing the ability to correct additional errors that might occur. Nevertheless, these chips could be used for internal testing while chips that are fully functional will be shipped to customers.

#### 2.4.2 Automatic Memory Generator

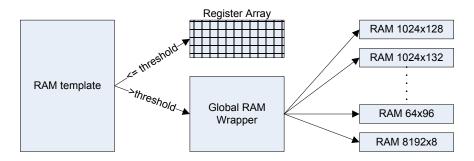

Since it is not feasible to instantiate the correct RAM instance in every module it was necessary to support a parametrizable flow for flexibility reasons. The final mapping to the RAM building blocks should be non-transparent to the designers. This is especially the case for FIFOs that are usually used with parameters for both width and depth, but also many other modules in EXTOLL can be changed with parameters which would result in different RAM configurations. In order to keep the underlying changes invisible several steps are needed.

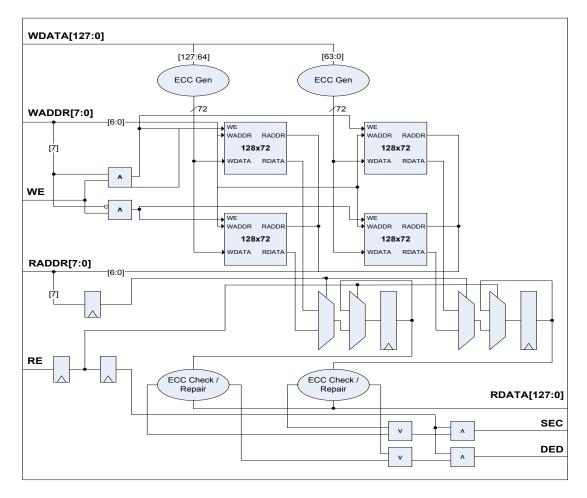

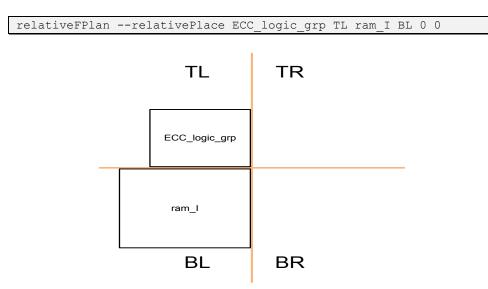

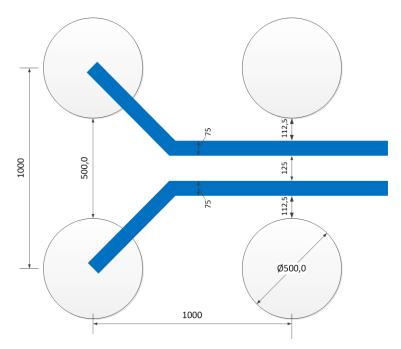

At first, a RAM building block for every single RAM configuration must be built. As mentioned before only a small number of core blocks is available, all other configurations must be built from these blocks. Because manual generation is both error-prone and tedious an automatic approach was selected. A Perl [44] script takes the desired width and depth of the RAM, analyzes which core block is most suitable and generates the Verilog code for the resulting RAM. The following figure 2.9 shows the internal structure of a selected RAM configuration.

As stated in the previous paragraph ECC functionality is essential. Thus, the best approach is the inclusion of ECC generation as well as ECC checking and error correction in the RAM instance itself. This means that on the interface level the RAM looks standardized with a read port and write port while all the ECC handling is hidden inside. In figure 2.9 a 256x128 configuration is built from 4 single 128x72 core blocks. 128 bits of data that will be written to

the RAM are split in two 64 bit wide streams that are separately protected through ECC. This adds additional 8 bits per data stream so that in the end 144 bits will be written. Because the core blocks only have a depth of 128 entries instead of 256 a second row of RAMs had to be added. The lower bits of the write address select the correct entry in the core block while the highest bit of the address together with the write enable signal select the row to which a new entry will be written.

A read operation is performed in a similar way, but it requires a little bit more logic. The lower bits of the read address are applied to all core blocks simultaneously. The highest bit of the read address which is delayed by a register stage to compensate for the read latency of the RAM controls a multiplexer for each column that selects the correct row that must be read. This multiplexer is followed by a register stage which is only updated if the read enable signal is asserted. This allows the RAM to retain the value of the read port even if the applied read address changes although no new read cycle was indicated through the read enable signal. Each 72 bits wide bus is then fed through the ECC check and repair logic. The resulting 64 bit data streams are then concatenated to the 128 bit read data port. The ECC logic also gives two indicators called *sec* (single error correct) or *ded* (double error detect) that can be connected to the register file, for example, to show that an error condition occurred during operation.

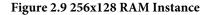

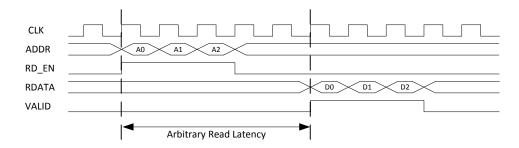

From a timing perspective some special characteristics have to be considered. Both ECC generation in the write path and ECC checking in the read path take some time as seen in figure 2.8. For writing this means that the propagation delay of the ECC generator must be added to the setup time of the internal RAM blocks. In a well designed logic block this should be no problem because the write data port will be driven by a register. Despite being a bad design style the RAM instance is not output registered. This is caused by the fact that the logic in EXTOLL was designed with FPGAs in mind and therefore optimized for the read latency of a block RAM in an FPGA. An additional cycle of read latency would break the following logic. By not registering the RAM output both ASIC and FPGA RAM blocks have the same read latency. However, the time needed to check and probably correct the read data is time that is missing in the next pipeline stage. Since a large part of a clock cycle is taken up by the ECC logic the next stage can only perform small logic functions without breaking timing. Nevertheless, in most cases this is not a problem because many RAMs are actually used in FIFOs which include some additional register stages behind the RAM to support fallthrough functionality. Regardless, for future projects it would be helpful to introduce a handshake mechanism with a read enable signal and a subsequent valid acknowledgement from the RAM as seen in the timing diagram in figure 2.10. This allows the surrounding logic to work without relying on the exact timing parameters of the underlying technology since it now does not have to adhere to a specific latency that is defined beforehand. An additional pipeline stage for ECC checking could have been easily hidden in that case with the result of a much more relaxed timing budget.

Figure 2.10 RAM Timing with Handshaking

In a second step another Perl script takes all the generated RAMs and builds a global RAM wrapper for them. This is a parametrizable Verilog module that will instantiate the correct RAM instance depending on the parameter set that is passed. If no matching RAM is found it will throw an error in simulation so that the missing module can be identified easily.

Finally, a set of RAM templates exist for both ASIC and FPGA. They provide an identical interface for both technologies and are used whenever a RAM is instantiated in the design. For small RAM sizes the RAM template does not map the configuration to a set of hard macros as described before but it builds an array of registers which is more efficient for small storage blocks. The threshold can be changed, but is set to a size 1024 bits by default. Altogether, the memory flow contains several levels of indirection as depicted in figure 2.11.

Figure 2.11 Levels of Indirection

Three different templates are currently supported:

#### - 1R1W1C (1 read, 1 write, 1 clock)

This is probably the most common configuration because it is usually needed in FIFOs. It consists of separate read and write ports and works with a common clock. All generated RAMs are dual-port RAMs with both a read and a write clock. In order to map the template to the underlying RAM the common clock is simply connected as the read and write clock.

### - 1R1W2C (1 read, 1 write, 2 clock)

This configuration is mostly needed for transfers between clock domains, commonly in asynchronous FIFOs. It directly maps to the underlying RAM.

#### - 2R1W1C (2 read, 1 write, 1 clock)

This configuration is only used in the register file when both software and hardware must be able to read data simultaneously. Since the RAMs only support a single read and a single write port they cannot be mapped directly. Instead, two 1R1W1C RAM templates are instantiated that are both written at the same time during a write operation. With two separate RAM instances inside that hold the same data a second read port can be offered, however with the penalty of additional area.

RAMs in FPGAs are always initialized and have a definite content. Unfortunately, this led to design mistakes at a few points in the EXTOLL logic that were coded with the assumption that this is always the case. However, RAMs in an ASIC are not initialized and can deliver an arbitrary value. For these cases, a special instance of the 1R1W1C wrapper was designed that performs an initialization of the RAM after the reset signal is deasserted by overwriting each row with a default value. During the time that is needed for this procedure (as many clock cycles as there are entries in the RAM) the RAM cannot be written to or read from. BIST operation will not be impaired by this functionality since it accesses separate test ports and the normal ports are disabled.

Generally, a RAM does not support reading and writing on the same address in the same clock cycle. If it still happens due to badly designed logic, the resulting read data is corrupted and might not reflect the value from the RAM. Logic should be aware of this issue and avoid these situations. Nevertheless, this problem can occur in EXTOLL because some instances are defined with a constant read enable signal and an address overlap will happen sooner or later. For these RAMs the wrappers support an extra parameter that will add supporting logic to perform a RAW (read-after-write) operation. By setting the parameter the write data will be forwarded to the read port in the case of an address violation. Instead of using the corrupt

value from the RAM the data that will be written in the same cycle is delivered on the read port and the hazard situation is avoided. This is also the behavior of an FPGA RAM and will not break the logic around it.

The automatic generation of the memory wrapper and the separate RAM instances is a valuable tool for a more efficient ASIC design. More than 20,000 lines of Verilog code were generated. If an error is found a small change in the underlying Perl code is sufficient and all RAMs are rebuilt with the fix in a matter of seconds. If a new core RAM block was introduced rerunning the tool would automatically check if building a RAM with the new core block is more efficient and rewrite the RAM accordingly.

# 2.5 Design for Test

FPGAs are reconfigurable by design. ASICs on the other side are hardwired and cannot be changed later on. Therefore it is important to make important parameters in the design reconfigurable in the ASIC by moving them to the internal register file so that they are changeable. The stored data can be divided into two categories:

#### - Initialization values

These are needed to bring up the design to a functional state and cover parameters for the host interface or the internal PLL. A misconfiguration at this stage might cause the chip to be unusable.

- Debug values

Several FSM states, counters and other valuable debug information from each unit are also stored in the register file.

Usually, register file access is done by system software. If the design is not able to bring up the host interface, for example, there is no way to get the system up and running. Therefore it was important to introduce a mechanism to change these values early on. Thus, the Debug Port contains an SPI [45] master that connects to an external flash memory. This flash can be filled with addresses of registers and their updated values. The internal protocol engine makes sure that all relevant registers can be updated before the chip continues its internal operation. By doing this, critical initial values of the design can be fixed.

The Debug Port also includes a second mechanism to access the register file. An I<sup>2</sup>C [46] slave allows external hardware to connect to the register file and read and write its values. There are twofold applications for this. For one, it allows reading debug values even after the

host system crashes which removes the normal operation mode of simply reading the register file from the CPU. This might give invaluable insight to the current state of the design, something which is a lot easier in an FPGA with tools like ChipScope [47] or SignalTap [48]. On the other hand it also allows an external management controller to read status values continuously from the device to monitor correct functionality or collect overall system statistics.

Both mechanisms access the register file via the SNQ interface. In order to offer fair access to both the SNQ and the Debug Port an arbiter was built in front of the register file's SNQ interface to manage concurrent access requests from both units. Since the loading mechanism from the flash is only executed shortly after power-up it will not impair the further operation. The following figure 2.12 [20] summarizes the datapaths inside the module.

Figure 2.12 Debug Port Overview

# 2.6 Clocking

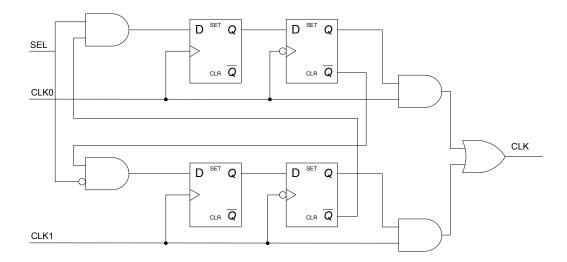

Clocking is besides reset the most important functionality in an ASIC. For maximum redundancy EXTOLL contains many clocking options so that each stage in generating the system clock can be bypassed and, if required, supplied externally from an on-board clock source like a high-frequency oscillator.

#### 2.6.1 Supporting Circuits

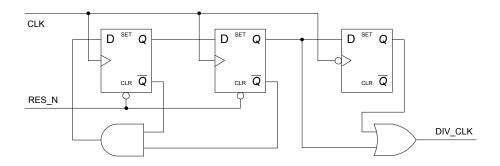

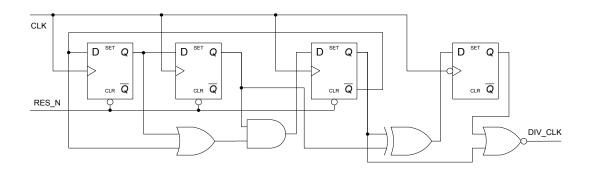

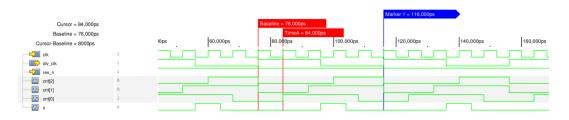

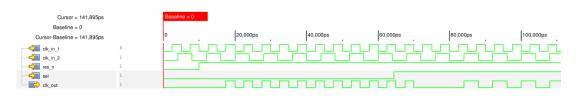

There are many cases where a system clock has to be divided down to a slower clock. If the relationship between the two clocks is a power of two this can be easily accomplished with a simple binary counter. The easiest case of a by-2 clock divider is a single flip-flop that inverts its output every clock cycle. Simple odd integer clock dividers [49] have the problem that they do not generate a 50% duty cycle. The following figures 2.13 and 2.15 show two clock dividers used in EXTOLL that will generate a 50% duty cycle together with their respective waveforms in figures 2.14 and 2.16. The correct duty cycle is achieved by generating two waveforms that are phase shifted by using a flip-flop that is triggered on the negative edge of the source clock which are then logically combined to form the resulting waveform.

Figure 2.13 Divide-by-3 Clock Divider

Figure 2.14 Divide-by-3 Clock Divider Waveform

A popular circuit for generating clock odd integer clock dividers is the Johnson counter [50]. It consists of a ring buffer built with a shift register. The inverted output of the last register is fed back to the input of the first stage.

Figure 2.15 Divide-by-5 Clock Divider